Commits on Source (184)

Showing

- .gitignore 1 addition, 0 deletions.gitignore

- README.md 1 addition, 0 deletionsREADME.md

- eagle/README.md 28 additions, 0 deletionseagle/README.md

- eagle/eagle_png.py 185 additions, 0 deletionseagle/eagle_png.py

- eagle/fab.lbr 3841 additions, 180 deletionseagle/fab.lbr

- eagle/fabcity-designrules.dru 73 additions, 0 deletionseagle/fabcity-designrules.dru

- eagle/img/.gitkeep 0 additions, 0 deletionseagle/img/.gitkeep

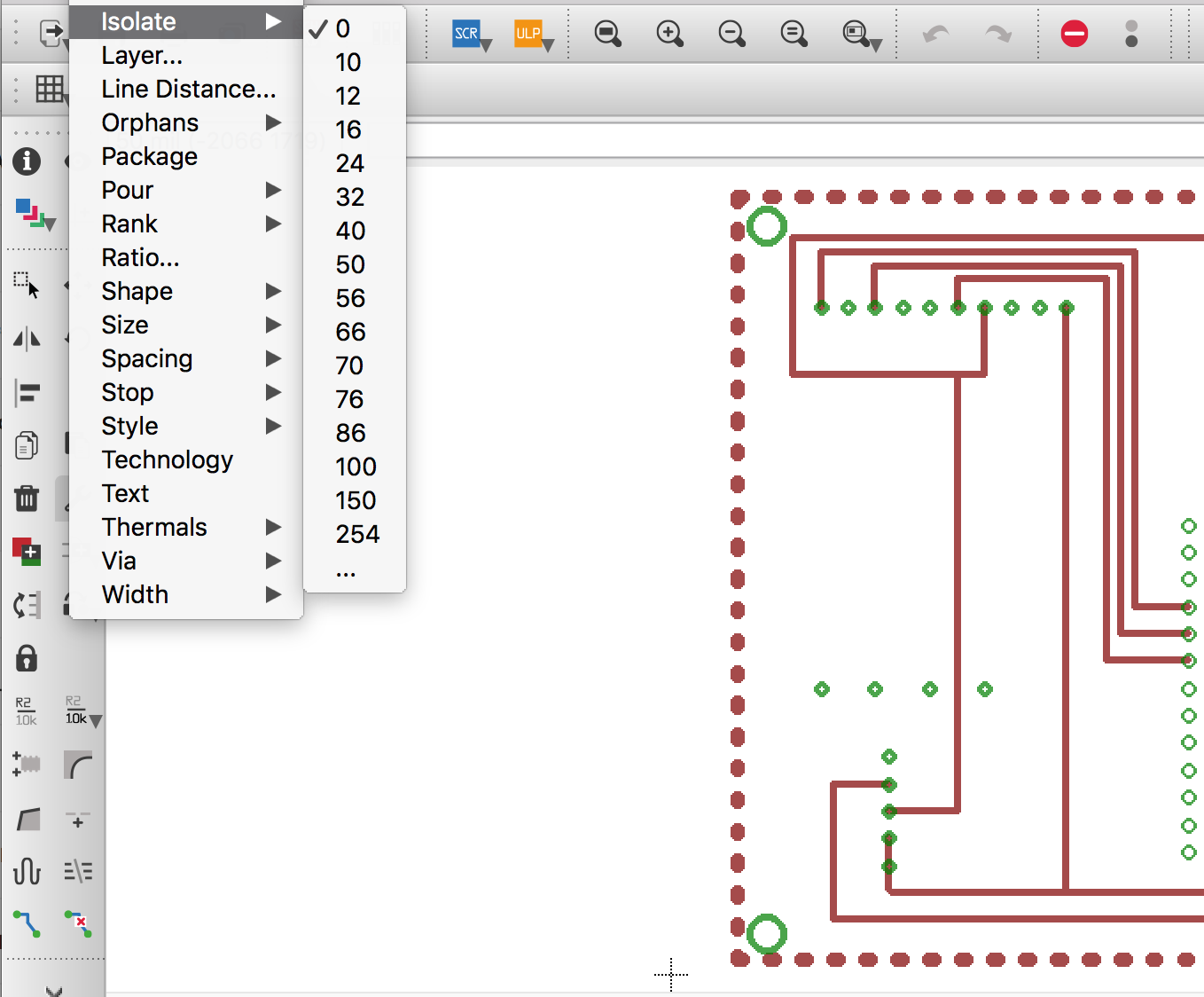

- eagle/img/isolate.png 0 additions, 0 deletionseagle/img/isolate.png

- index.html 11 additions, 3 deletionsindex.html

- kicad/README.md 23 additions, 0 deletionskicad/README.md

- kicad/archive/fab.lib 0 additions, 0 deletionskicad/archive/fab.lib

- kicad/archive/fab.mod 0 additions, 0 deletionskicad/archive/fab.mod

- kicad/archive/fab.pretty/fab-1X06SMD.kicad_mod 15 additions, 0 deletionskicad/archive/fab.pretty/fab-1X06SMD.kicad_mod

- kicad/archive/fab.pretty/fab-2-SMD-5X3MM.kicad_mod 17 additions, 0 deletionskicad/archive/fab.pretty/fab-2-SMD-5X3MM.kicad_mod

- kicad/archive/fab.pretty/fab-2X02SMD.kicad_mod 13 additions, 0 deletionskicad/archive/fab.pretty/fab-2X02SMD.kicad_mod

- kicad/archive/fab.pretty/fab-2X03.kicad_mod 67 additions, 0 deletionskicad/archive/fab.pretty/fab-2X03.kicad_mod

- kicad/archive/fab.pretty/fab-2X03SMD.kicad_mod 15 additions, 0 deletionskicad/archive/fab.pretty/fab-2X03SMD.kicad_mod

- kicad/archive/fab.pretty/fab-2X04_THRU.kicad_mod 19 additions, 0 deletionskicad/archive/fab.pretty/fab-2X04_THRU.kicad_mod

- kicad/archive/fab.pretty/fab-2X05SMD.kicad_mod 19 additions, 0 deletionskicad/archive/fab.pretty/fab-2X05SMD.kicad_mod

- kicad/archive/fab.pretty/fab-3.5MMTERM.kicad_mod 18 additions, 0 deletionskicad/archive/fab.pretty/fab-3.5MMTERM.kicad_mod

.gitignore

0 → 100644

README.md

0 → 100644

eagle/README.md

0 → 100644

eagle/eagle_png.py

0 → 100644

Source diff could not be displayed: it is too large. Options to address this: view the blob.

eagle/fabcity-designrules.dru

0 → 100644

eagle/img/.gitkeep

0 → 100644

eagle/img/isolate.png

0 → 100644

204 KiB

kicad/README.md

0 → 100644

File moved

File moved

kicad/archive/fab.pretty/fab-2X03.kicad_mod

0 → 100644